|

|

|

www.design-reuse-embedded.com

www.design-reuse-embedded.com |

|

Addressing Three Critical Challenges of USB Type-C Implementation

USB技术市场营销经理Morten Christiansen, May. 10, 2016 –

USB是用于个人和消费电子产品的最为流行的有线连接标准。每年生产的具有USB功能的产品超过20亿台。在 过去的15年内,出现了使USB众多的性能升级,新型USB Type-C™引入了一种可扩展、强健和用户友好的微型 连接器,其势头仍将持续今后的15年。USB Type-C的成功获得首肯;USB Type-C标准已成为采用速度最快的 USB标准,在2014年发布了规范的数月内,就有多种产品问世。

采用USB Type-C连接的产品具有用户接口友好的特点,原因很多。在主机一侧和设备一侧的连接器不存在差 别;通用电缆适合于所有产品;可翻转连接器,并以任何方式插入;插口小,是便携产品的理想选择。此外,USB Type-C电缆通用扩展转接口支持插座/显示可提供明显更低的系统成本,与现有的专用扩展插座相比,复杂性更 低。典型的扩展插座包括,一个DisplayPort中继器和USB集线器,通常用于连接键盘和鼠标,也能支持联网、扬 声器输出和模拟耳机。扩展转接口插座显示配有内置的USB集线器,USB功能也能适用DisplayPort交替模式。 同时,DisplayPort HBR-3比特率可同时支持具有USB 3.0或USB 3.1的4K/60Hz显示。通过在扩展插座或对接 显示设备时增加功率输出,USB Type-C是可用于功率、数据、视频和音频的唯一连接器。

设计人员门正积极忙碌于设计具有USB Type-C支持的新产品和系统芯片。在本白皮书中,介绍了在设计USB Type-C产品以及具有USB Type-C支持的SOC方面所面临和关键挑战和建议的解决方案。

- 第一项挑战:支持与USB Type-C连接器的一个或另一方位相匹配的双超高速数据通道。

- 第二项挑战:分离SoC和系统设计,支持具有USB Type-C功能相关产品硬件的多种变体。设计人 员必需了解关于精密模拟电路和高压/高电流开关的规范要求,它们可能是外部分离部件、外部专用 USB Type-C控制器芯片,也可能集成在电源管理IC中或SOC中。

- 第三项挑战:分离额外的USB Type-C管理软件,所述软件可在主处理器、内部微控制器上执行,或在 电源管理IC中的微控制器上执行,或在外部专用USB Type-C芯片上执行。

挑战1:数据通道实施

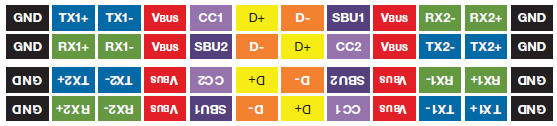

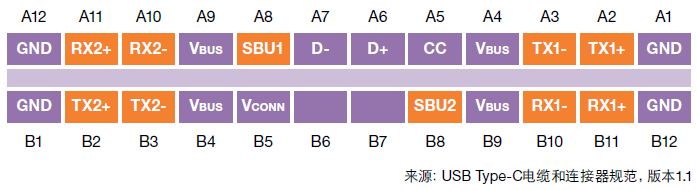

USB Type-C连接器是对称的,它复制了大多数信号,使其支持可翻转性,如图1所示。

图1:USB Type-C引出线和旋转对称

对于这类复制,需要支持超高速USB产品的数据通道多路复用器,以及支持交替模式产品的数据通道交叉开关。对于USB Type-C数据通道,设计人员可选择四种实施方案:外部数据通道开关;实施双PHY或双端口;适用内部片上开关;或使用USB-C 数据通道PHY。

外部数据通道开关

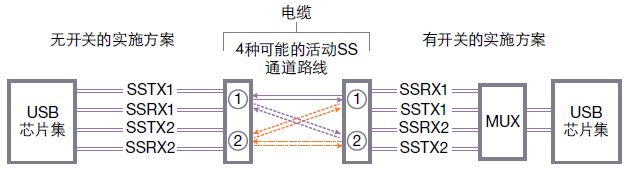

外部数据通道开关(或多路复用器,位于SoC或USB芯片集外部 ,请参见图2)常用于支持USB Type-C的商业产品中。现有的高频模拟开关最初是为PCIe、Ethernet、SATA、DisplayPort和其他标准设计的,对其进行重新修改以用于USB Type-C。外部开关解决方案的主要优点在于能够以最快的速度推向市场。其缺点在于成本、PCB面积以及信号质量降低(与具体实施相关)。

图2:关于在基于USB Type-C的端口上实现数据总线路由的逻辑模型

开关中的损失,会影响从USB端口至USB Type-C连接器的总通道损失。对于USB 3.0(正式名称为工作在USB 3.1 Gen1模式下的USB 3.1端口),开关损失(包括丢包)的典型值为1.5dB。对于USB 3.0 Type-C,总通道损失为6.5dB。多出的5dB总通道损失会使从USB端口到连接器的最大PCB路径长度降低至6-7",具体情况取决于PC的质量和PCB布局。对于某些产品,5dB的通道损失可以接受。然而,对于采用标准A的主机,总通道损失为10dB,对于很多主机实施方案来说,10dB的通道损失都是一项不低的挑战,5dB的通道损失不可能实现。

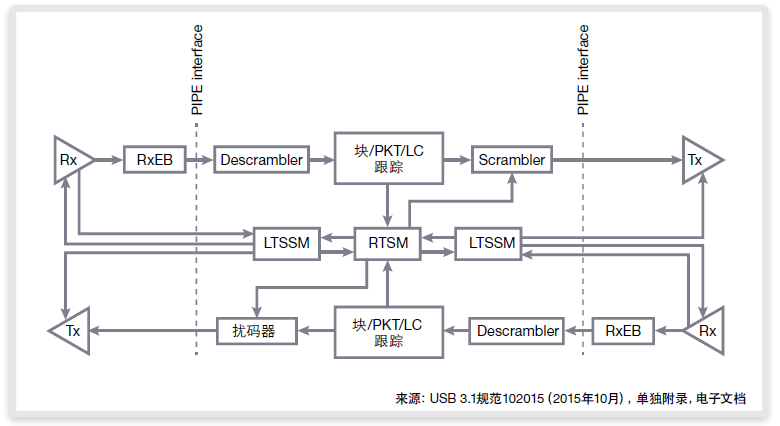

对于USB 3.1(工作在USB 3.1 Gen2模式下的USB 3.1端口),从芯片到连接器的通道损失是8.5dB。典型的PCB路径距离为4",但当增加外部开关时,可将PCB路径降至2"或更低。通过采用无内置转接驱动器的外部USB Type-C开关,部分产品可支持USB Type-C(图3)。对于USB 3.0来说,这是恰当的;然而,对于USB 3.1 Gen2模式,所需的转接驱动器为完整的重定时器,它由两个完整的PHY以及大量数字电路构成。对于USB 3.1的成本和功耗,这都会产生不利影响。

图3:USB 2.0操作中的高水平重定时器体系结构实力

双PHY或双端口解决方案

对于支持USB Type-C的SOC,实施双USB 3.0 PHY或USB 3.1 PHY是能够在最短时间内推向市场的解决方案。一个或另一个PHY处于活动状态,这取决于USB Type-C连接器的方位。另一PHY处于低功率状态。无外部数据通道开关,无信号质量损失。即使在具有较大硅面积的情况下,与外部开关或开关加转接驱动器相比,该解决方案的成本更低。

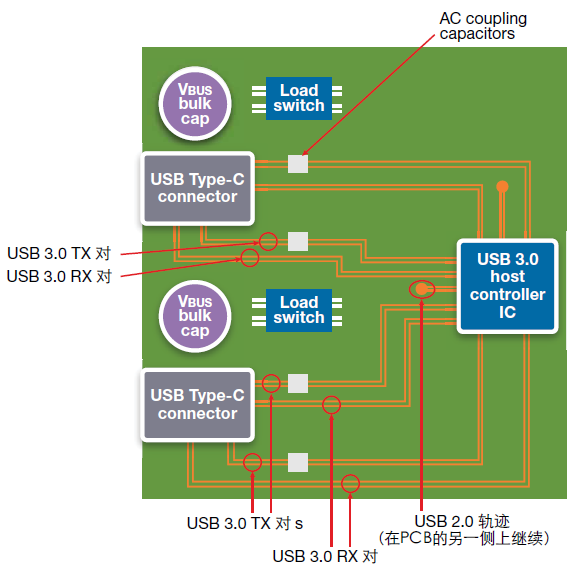

对于多端口USB主机,采用了该解决方案的一种变体:使用两个关于标准A的现有端口,以创建1个USB Type-C端口。在图4中,显示了在2端口USB Type-C主机控制器插件板中,使用的公用4端口USB 3.0主机控制器芯片。对于1个USB Type-C 连接器,采用了两个超高速USB RX和TX对。为保持信号完整性,超高速信号直接从控制器导向USB Type-C连接器。在PCB的可视的一侧能够清楚看到路由布线。两个USB 2.0信号对也从控制器传向USB Type-C连接器。USB 2.0 PCB布线并非很关键,布线在PCB的另一侧上继续,以免干扰超高速USB PCB轨迹的最优路由布线。

USB Type-C规范要求,在连接装置之前不得启用Vbus。在USB Type-C连接器旁边可见到负载开关和大电容。在主机的每一CC插针上具有一个上拉电阻Rp。连接了装置时,装置上的下拉电阻Rd会使1个CC上的电压降低。这样,负载开关就能启用Vbus。在正常情况下,使用CC插针检测来确定方位。在图4显示的该设计方案,无需方位检测。两个端口均处于活动状态,但仅有一个端口会检测装置。另一端口虽处于活动状态但并未被使用。该方法的功率损失较小,对于桌面PC或便携式电脑,这是可接受的。

图4:多端口USB Type-C主控制器PCB

USB Type-C仍是市场上较新的,对于快速推向市场的产品,其利润率较好。适用双Type-C连接器,双PHY/双端口设计取代了4个标准A连接器,在最低成本下,增加了2个Vbus负载开关,使用的电阻和电容更少。

在具有USB Type-C端口的笔记本电脑中,常使用"用于1个USB Type-C端口的2个标准A端口"。典型情况下,芯片集支持多个USB端口。仅使用USB的装置以及双功能产品也采用了双端口方法。如果仅使用1个USB控制器,仍需要方位检测和数据通道开关。然而,数据通道开关位于USB控制器和双PHY之间的数字域内,因而不影响信号质量。

内部片上开关

作为对外部数据通道开关的替代,另一方式是芯片/片上开关。与外部开关相比,该方案的损耗更低,对于10 Gbps USB 3.1 Gen2模式操作尤其有用。然而,实施针对USB 3.1 Gen2模式的片上开关较为困难,这是因为,开关必须补偿非线性频率和相位响应。此外,开关不得允许下述高振幅显示端口、USB TX以及低振幅USB 3.1 RX信号之间的串扰。需要具备阻抗匹配以防止反射。对于无转接驱动器电路的片上开关,仅对USB 3.1 Gen1 (USB 3.0)模式和DisplayPort HBR-2才是可行的。

USB-C PHY

外部开关具有最快推向市场的特性,但会增加成本,双PHY方案使用了过大的硅面积,内部开关仅对USB 3.0才有现实意义。对于SOC集成,推荐的方案是采用单个可靠的USB-C PHY,以降低风险,并将硅面积最小化。

Synopsys宣布了多种采用先进工艺节点、针对USB 3.0和USB 3.1的USB-C PHY产品。DesignWare USB-C 3.1和3.0 PHY均为双通道方案,优点与双PHY方案相同。无模拟开关,信号质量不会降低。根据USB Type-C连接器的方

位,根据需要,某一通道或另一通道将处于活动状态。DesignWare USB-C PHY在两个通道之间共享了大量电路,与双PHY方案相比,在硅面积方面成本十分经济。

挑战2:硬件分割

并非所有的USB Type-C硬件和特性均能集成在单个通用SOC中,因此,对于成本、功耗以及使用相同SOC的面积效率产出,恰当的硬件分割十分关键。

对于ASIC和SOC设计人员,分割事宜始终是需要面临的挑战。在消费电子产品的早期岁月中,这类挑战仅是简单地将部件数目最小化。随着ASIC的演变,芯片组设计人员不得不将完整的系统功能分割成多个设备。SOC的出现可能会一劳永逸地结束分割方面的挑战事宜。然而,很多单芯片SoC并不是单片,而是在单个包上包含多个片,这是因为,将所有功能集成在单芯片SOC中并非可行,或并不经济。

对于单芯片SOC,尤其是在先进工艺节点中,对于高级消费电子产品,其经济性更低。典型情况下,在主SOC中去除了功率、音频和射频电路,原因在于,对于这类功能,使用不是很先进的工艺更为经济。与单芯片方案相比,多芯片方案可能更为经济,这是因为,它能提供额外功能和较高的价格点。

对于其理想的整个系统方案,SOC设计人员需解决复杂的分割挑战事宜。每一设计都有自己的理想方案:低成本、小尺寸、低功率、特性丰富以及高性能。然而,对于大多数解决方案,会在这些选择之间进行平衡。不幸的是,对于某一SOC设计而言的理想选项,对于另一SOC设计并不一定适合。因此,SOC设计人员仍需迎对分割方面的挑战:在单芯片SOC应包含些什么,或应将什么排除在外。

集成PHY --专用USB Type-C硬件之间的对比

对于标准USB实施,模拟音频、UART模式、OTG、电池充电和高速USB组合在USB 2.0 D+/D-插针上。这样,要想使用外部方案,将变得困难,而且并不经济。对于标准USB Type-C PHY,无论采用的工艺是什么,最优USB Type-C PHY方案是将其功能性和USB 1.1、USB 2.0或完整的USB 3.0或3.1 PHY集成在一起。对于USB Type-C硬件集成,关键挑战在于高压/高电流要求的5V电源容差。虽然一些USB Type-C硬件可集成在先进工艺节点内,但也需要外部负载开关,以及可选的Vconn和Vbus监测功能。在SOC上增加管脚、增加外部FET和其他电路会增大成本,与完整的USB Type-C端口控制器芯片相比,该方案的经济性较差。

在解决硬件分割挑战事宜方面,USB Type-C规范为设计人员提供了足够的灵活性。配置通道(CC)管脚用于向主机或装置发送信号,具有电流功能、方位确定和功率输出特性,它们与USB管脚是分开的。通过与CC管脚相连的电路,可实现连接检测,在连接实现之前允许产品禁用USB功能,以便节省电能,在便携式产品中,该点十分重要。电缆中仅有1条CC线。这样,与电缆每一端上CC管脚相连的电路就能确定连接器极性。

功率输出是USB Type-C规范的特性之一,使用它,对于采用使用USB Type-C连接器的产品,可提供高达100W的功率。功率输出消息(PD消息)用以发现电压和电流能力,复用CC管脚。使用PD消息,Vbus电压可从5V增加到12V或20V,电流可从标准USB(500mA或900mA)增加至2A、3A甚至5A。除了功率输出之外,还采用了PD消息来支持动态数据切换,亦即,在USB主机和设备之间进行变换,发现并配置交替模式。

对于USB Type-C产品所需的CC逻辑,在某些时候可将其集成在SOC中。对于高电流能力,功率管理IC(PMIC)中的集成是最佳解决方案。为了最快推向市场,可使用外部芯片实现。

USB Type-C规范为设计人员提供了更多的实施选择。设计人员可针对不同产品类型选择方案,创建最经济、最节能和面积最小的系统解决方案。

USB Type-C端口控制器接口

在USB Type-C端口控制器接口(TCPCI)规范中,定义了用于USB Type-C端口的硬件和低级软件分割,提供了处理硬件分割挑战的解决方案。单独的USB Type-C端口控制器(TCPC)包含用于CC和PD消息功能的所需低级硬件。TCPC可以在SOC外部,可作为外部芯片,集成在PMIC中,或作为集成方案使用在SOC中。

众多供应商发布了数十种USB Type-C支持芯片。在部分芯片中,仅实施了简单的CC逻辑,在另一些芯片中,增加了PD消息功能并包含USB Type-C端口控制器(TCPC)接口,在一些芯片中,甚至还包含微控制器以及作为USB Type-C 软件分割可能解决方案的SW栈。

挑战3:USB Type-C软件分区

第三项挑战是,如何分割与具体产品相关的USB Type-C软件。USB Type-C端口管理器(TCPM)软件可以是操作系统(OS)的一部分,可以是与产品相关的驱动器模块,SOC中的嵌入软件,或外部微控制器的固件。

根据OS厂家,假定无需改变现有的USB软件栈和USB控制器接口,设计人员可采用嵌入式操作系统(OS)以支持USB Type-C以及其交替模式。

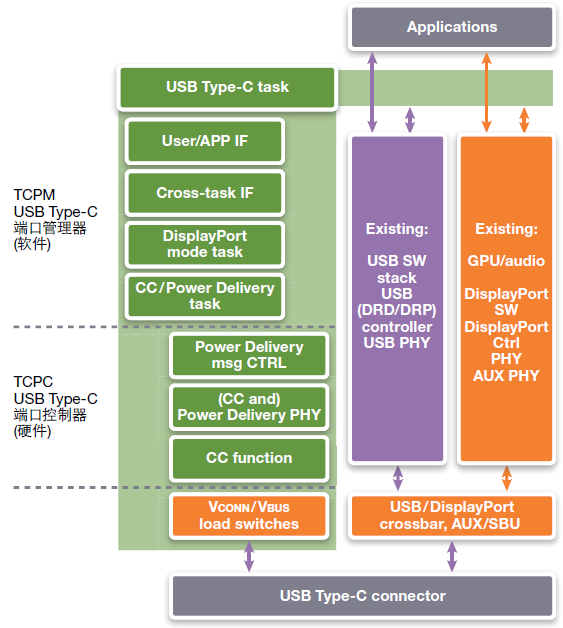

相同假设也适用于显示端口或其他交替模式,即使显示端口软件和硬件标准不存在也同样。在交替模式下,允许重新确定USB Type-C连接器上大多数插针的功能,使其适用于MHL、显示端口、或Thunderbolt™ 3(例如),请参见图5。

图5:可交替模式中重新设定功用的管脚

在USB Type-C端口控制器接口和USB Type-C系统软件接口规范中,将高级USB Type-C软件定义为单独的USB Type-C任务,从而使得USB Type-C 更容易实施,也更容易扩展(图6)。无需对操作系统进行大的改动,就能支持多种应用和划分,从而缩短了推向市场的时间。

图6:USB Type-C任务划分和功能

借助TCPCI和USB Type-C系统软件接口规范的特性,在面对USB Type-C软件分割挑战方面可提供多项便利。当将USB Type-C功能置于在软件中时,所述软件在产品开发过程中不断更新,在开发过程中可发现与USB Type-C相关的事宜,从而降低设计和展示风险。

USB Type-C端口管理器

USB Type-C端口管理器(TCPM)是一种软件组件,它能运行在TCPC中的微控制器(MCU)上、PMIC或SOC上。对于很多类型的产品,TCPM也能运行在SOC中的应用处理器上。对于特定类型的产品,可用高级TCPC硬件取代TCPM。例如,USB 3.0设备总会启用设备模式的下拉电阻,检测连接器方向属性,并将信号发送至USB Type-C 数据通道开关。显示端口交替模式产品必需发现交替模式功能,然后恰当地配置交叉开关和USB功能。

解决三种USB Type-C挑战

对于USB 2.0设计,可使用现有的PHY,添加简单的USB Type-C硬件和软件即可。根据具体产品的能力,复杂程度差别很大,从双电阻到可交换电阻和电压比较器,加上对现有USB OTG软件的USB Type-C的支持。

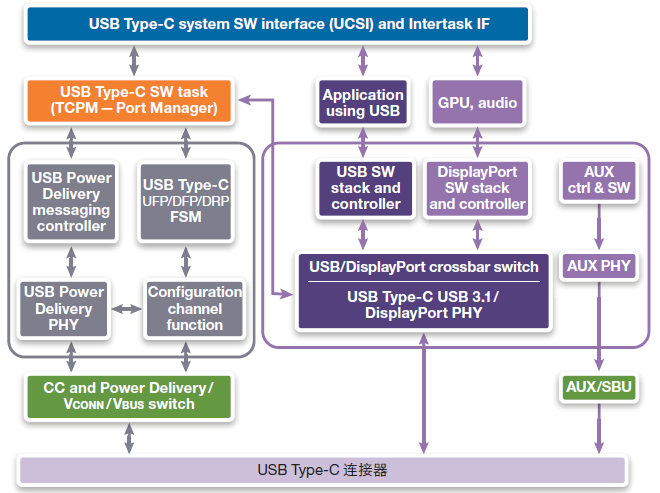

使用Synopsys针对USB 3.0和USB 3.1产品的DesignWare USB-C PHY,可帮助设计人员解决超高速USB和超高速10G数据通道方面的挑战。在USB-C PHY外部,必须添加与具体产品相关的USB Type-C硬件和软件。在将恰当且优

化的TCPC硬件及TCPM软件集成到PMIC或SOC之前,外部TCPC和TCPM产品可提供经济且能快速推向市场的解 决方案。此外,在Synopsys针对高级工艺节点的USB-C 3.1/DisplayPort 1.3 PHY中,采用不会降低信号质量的分线 器、而且不再需要外部转接驱动器。

图7:DesignWare USB-C 3.1 / DisplayPort 1.3 PHY替代了用于USB和DisplayPort的外部交叉开关

USB Type-C端口管理器(TCPM)可在USB旁边的应用处理器和DisplayPort软件栈上执行,如图7所示。此外,还能 将Vconn、Vbus和AUX/SBU开关集成在TCPC芯片内。通过恰当的USB Type-C硬件和软件分割,可降低总的系统成 本,降低实施风险,并加快推向市场的速度。

附加资源

- 文章 : 在高速USB产品中实现USB Type-C

- 文章 : 将现有的USB设计方案转换为支持USB Type-C的连接方案

- Webinar : 设计用于 USB Type-C产品的SOC

Back

Back Contact Us

Contact Us